# SYRCoSE 2016

## Editors:

### Alexander S. Kamkin, Alexander K. Petrenko, and Andrey N. Terekhov

Preliminary Proceedings of the 10<sup>th</sup> Spring/Summer Young Researchers' Colloquium on Software Engineering

Krasnovidovo, May 30-June 1, 2016

**Preliminary Proceedings of the 10<sup>th</sup> Spring/Summer Young Researchers' Colloquium on Software Engineering (SYRCoSE 2016)**, May 30-June 1, 2016 – Krasnovidovo, Mozhaysky District, Moscow Oblast, Russia.

The issue contains papers accepted for presentation at the 10<sup>th</sup> Spring/Summer Young Researchers' Colloquium on Software Engineering (SYRCoSE 2016) held in Krasnovidovo, Mozhaysky District, Moscow Oblast, Russia on May 30-June 1, 2016. The paper selection was based on originality and contributions to the field. Each paper was peer-reviewed by at least three referees.

The colloquium's topics include programming languages, software development tools, embedded and cyber-physical systems, software and hardware verification, formal methods, information security, and others.

The authors of the selected papers will be invited to participate in a special issue of '*The Proceedings of ISP RAS*' (<u>http://www.ispras.ru/proceedings/</u>), a peer-reviewed journal included into the list of periodicals recommended for publishing doctoral research results by the Higher Attestation Commission of the Ministry of Science and Education of the Russian Federation.

The event is sponsored by Russian Foundation for Basic Research (Project №16-07-20256).

## Contents

| Foreword ······6                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Committees                                                                                                                                          |

| Referees ······8                                                                                                                                    |

| Language Support for Generic Programming in Object-Oriented Languages: Design Challenges<br>J. Belyakova9                                           |

| Refinement Types in Jolie<br>A. Tchitchigin, L. Safina, M. Elwakil, M. Mazzara, F. Montesi, V. Rivera20                                             |

| Visual Dataflow Language for Educational Robots Programming<br>G. Zimin, D. Mordvinov                                                               |

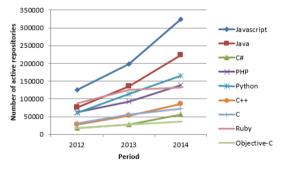

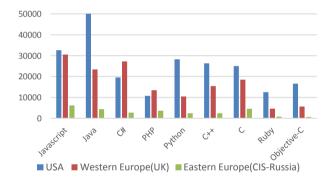

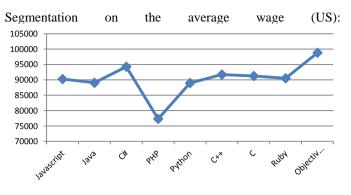

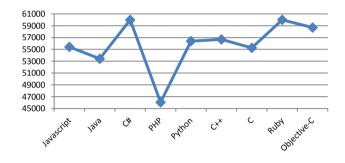

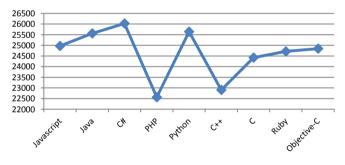

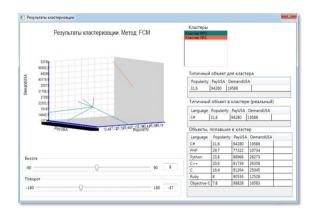

| Programming Languages Segmentation via the Data Mining Software "ShaMaN"<br><i>T. Afanasieva, S. Makarova, D. Shalaev, A. Efremov</i>               |

| Context-Based Model for Concern Markup of a Source Code<br>M. Malevannyy, S. Mikhalkovich                                                           |

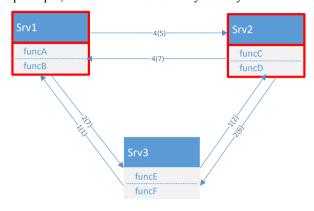

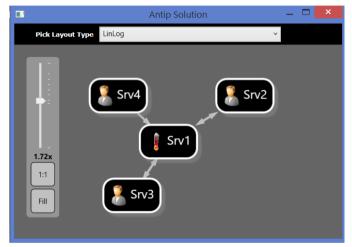

| Metric-Based Approach to Anti-Pattern Detection in Service Oriented Software Systems<br><i>A. Yugov</i>                                             |

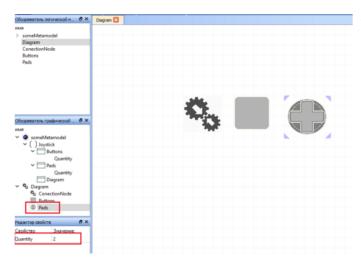

| Technology for Application Family Creation Based on Domain Analysis<br>A. Gudoshnikova, Yu. Litvinov                                                |

| Language for Describing Templates for Test Program Generation for Microprocessors<br><i>A. Tatarnikov</i>                                           |

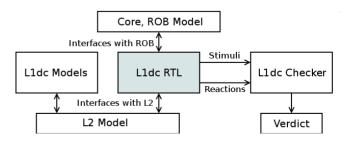

| Specification-Based Test Program Generation for MIPS64 Memory Management Units<br>A. Kamkin, A. Kotsynyak                                           |

| Approaches to Stand-alone Verification of Multicore Microprocessor Caches<br>M. Petrochenkov, I. Stotland, R. Mushtakov                             |

| Checking Parameterized PROMELA Models of Cache Coherence Protocols<br>V. Burenkov, A. Kamkin                                                        |

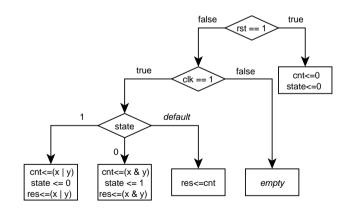

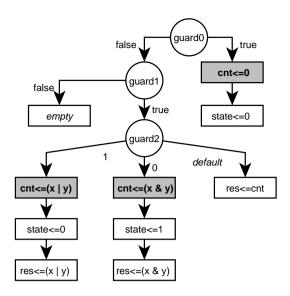

| A Model Checking-Based Method of Functional Test Generation for HDL Descriptions<br><i>M. Lebedev, S. Smolov</i>                                    |

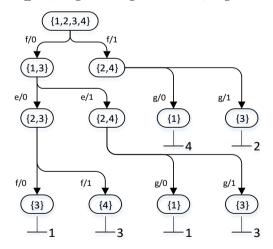

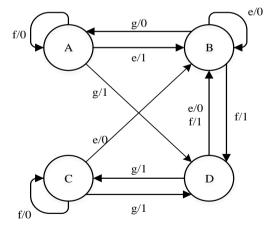

| Deriving Adaptive Checking Sequence for Nondeterministic Finite State Machines<br>A. Ermakov, N. Yevtushenko·····90                                 |

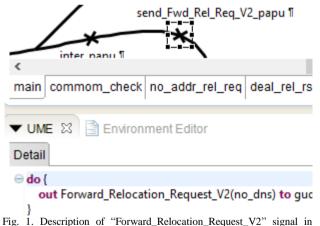

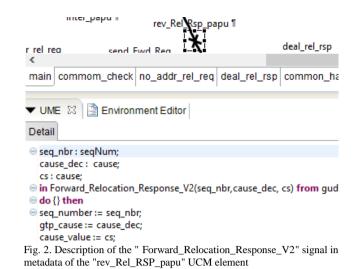

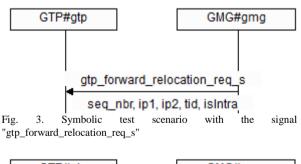

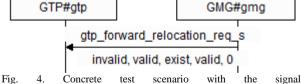

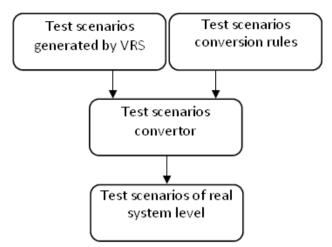

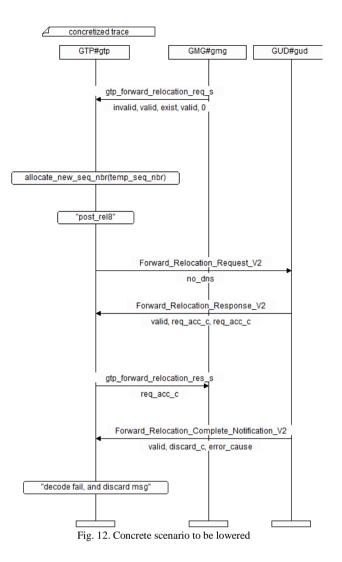

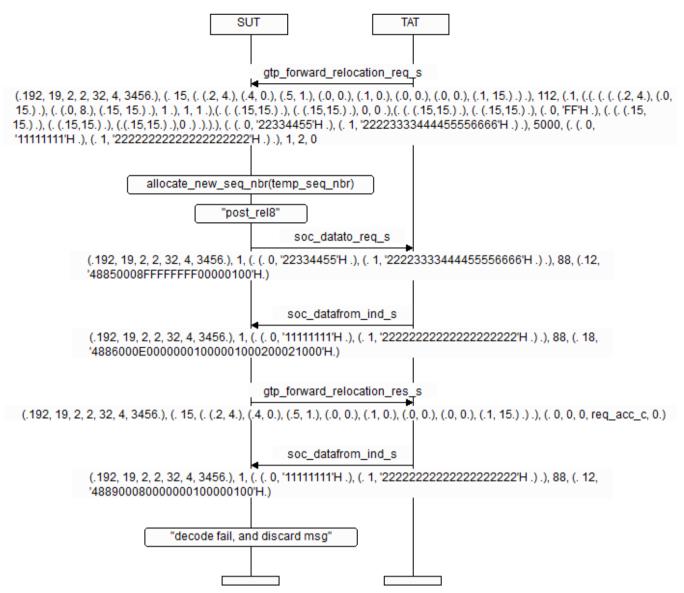

| Conversion of Abstract Behavioral Scenarios into Scenarios Applicable for Testing<br>P. Drobintsev, V. Kotlyarov, I. Nikiforov, N. Voinov, I. Selin |

| Automation of Failure Mode, Effects and Criticality Analysis<br><i>P. Privalov</i> 104                                                              |

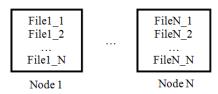

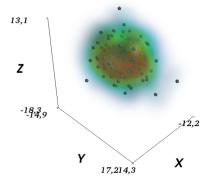

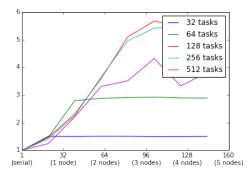

| Parallel Processing and Visualization for Results of Molecular Simulations Problems<br>D. Puzyrkov, V. Podryga, S. Polyakov                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

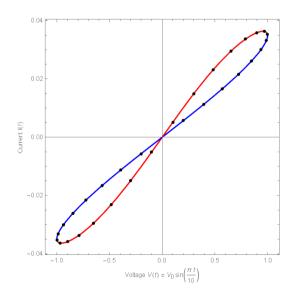

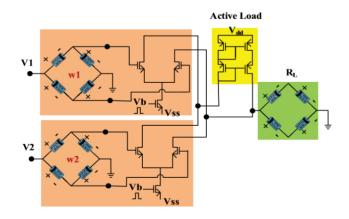

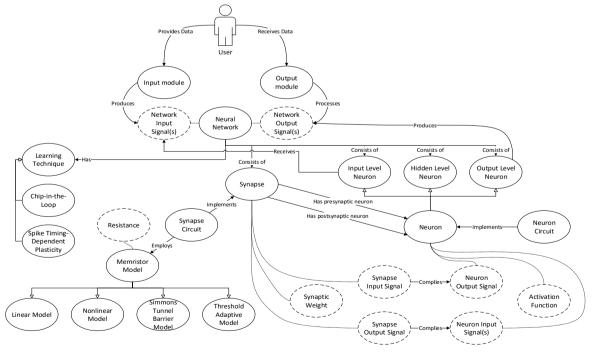

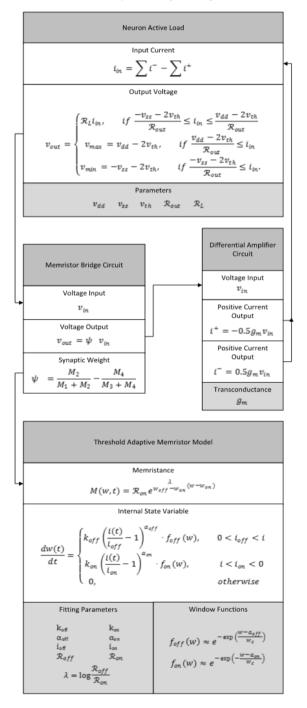

| Memristor-based Hardware Neural Networks Modelling Review and Framework Concept<br>D. Kozhevnikov, N. Krasilich                                                                  |

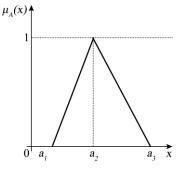

| A Method of Converting an Expert Opinion to Z-number<br>E. Glukhoded, S. Smetanin <sup>124</sup>                                                                                 |

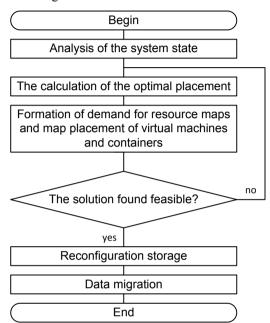

| Development and Research of Models of Self-Organization of Data Placement in Software-Defined<br>Infrastructures of Virtual Data Center<br><i>I. Bolodurina, D. Parfenov</i> 129 |

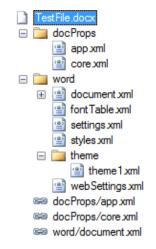

| Automated Text Document Compliance Assessment System<br>M. Zhigalova, A. Sukhov                                                                                                  |

| Complete Contracts through Specification Drivers<br>A. Naumchev, B. Meyer 141                                                                                                    |

| Usability of AutoProof: a Case Study of Software Verification<br>M. Khazeev, V. Rivera, M. Mazzara, A. Tchitchigin 149                                                           |

| Certified Grammar Transformation to Chomsky Normal Form in F*<br>M. Polubelova, S. Bozhko, S. Grigorev                                                                           |

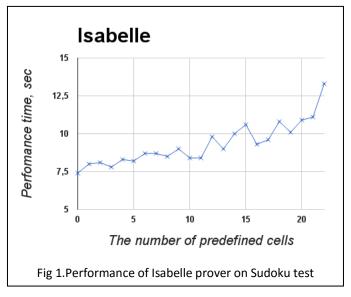

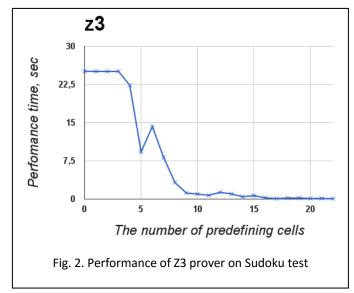

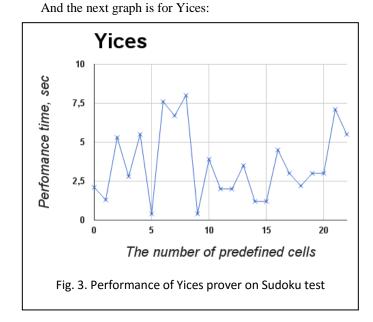

| Performance Testing of Automated Theorem Provers Based on Sudoku Puzzle<br>M. Sabyanin, D. Senotov, G. Skvortsov, R. Yavorsky                                                    |

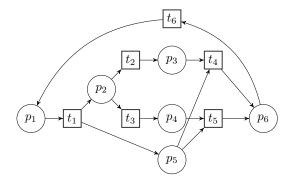

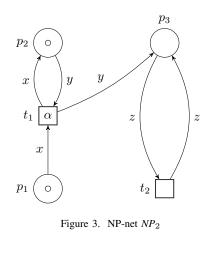

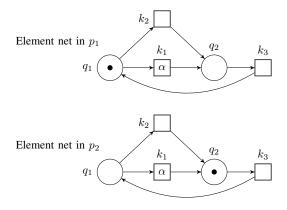

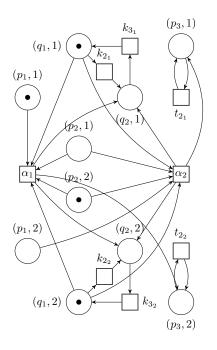

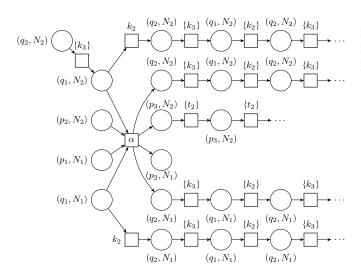

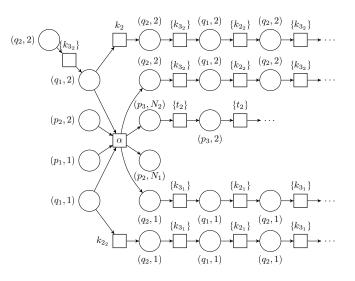

| Translation of Nested Petri Nets into Petri Nets for Unfoldings Verification<br>V. Ermakova, I. Lomazova                                                                         |

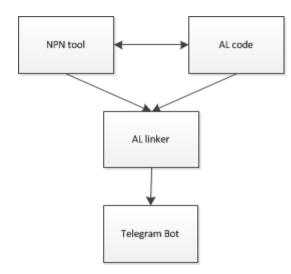

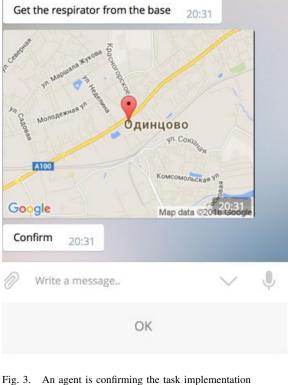

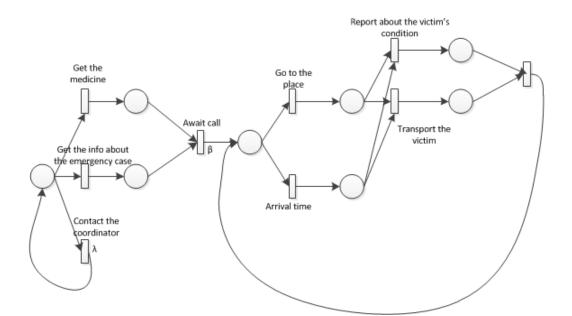

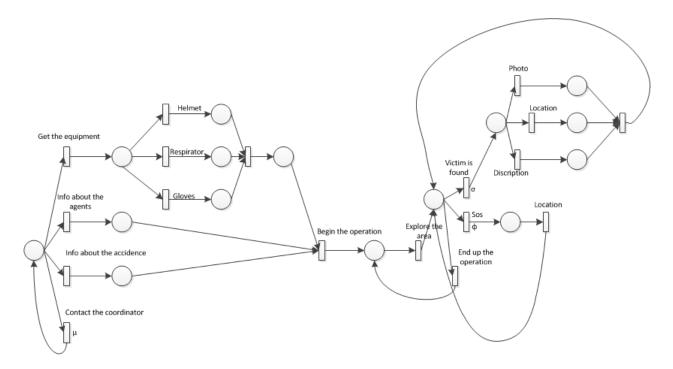

| Automatic Code Generation from Nested Petri Nets to Event-based Systems on the Telegram Platform<br>D. Samokhvalov, L. Dworzanski                                                |

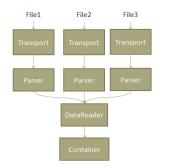

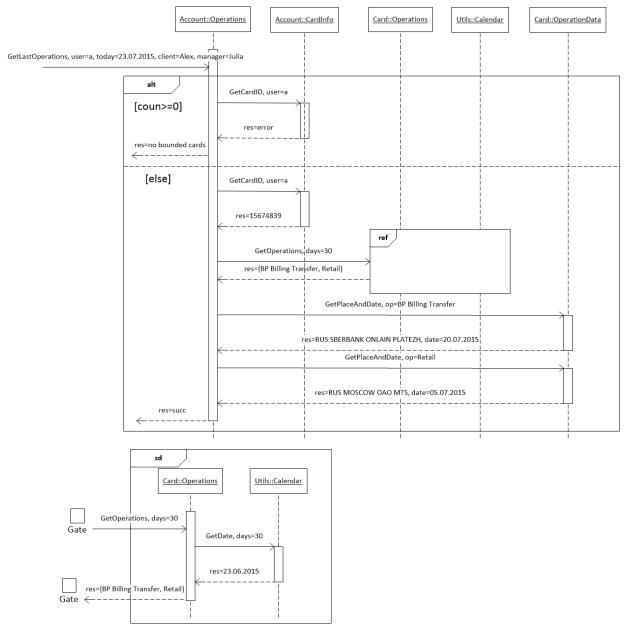

| Mining Hierarchical UML Sequence Diagrams from Event Logs of SOA Systems while Balancing between<br>Abstracted and Detailed Models<br><i>K. Davydova, S. Shershakov</i>          |

| Applying MapReduce to Conformance Checking<br>I. Shugurov, A. Mitsyuk                                                                                                            |

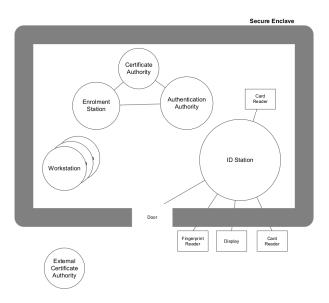

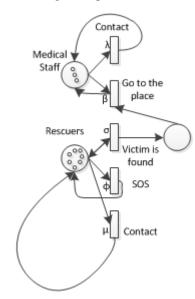

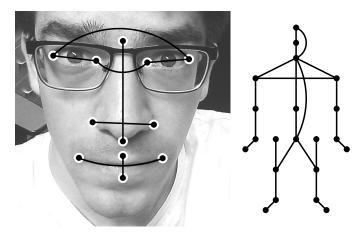

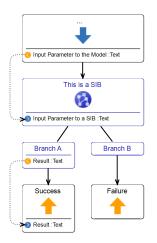

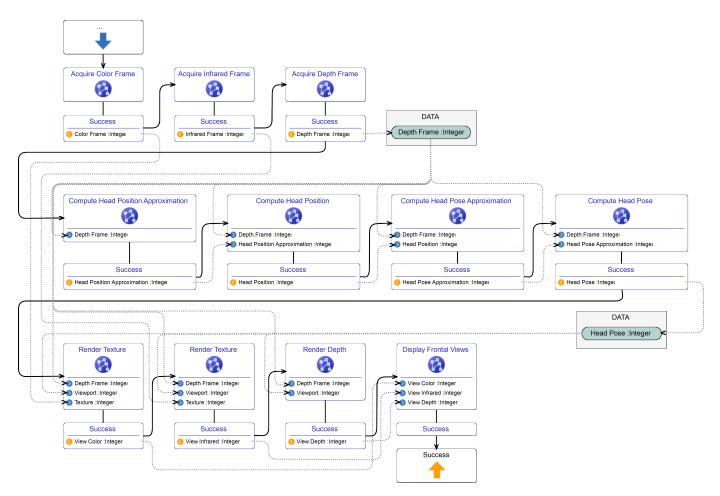

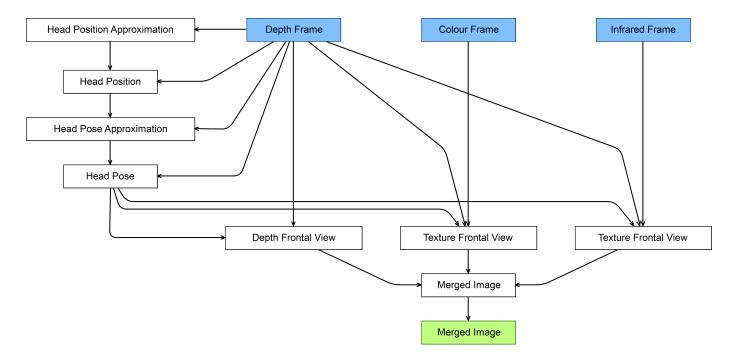

| Modelling the People Recognition Pipeline in Access Control Systems<br>F. Gossen, T. Margaria, T. Göke                                                                           |

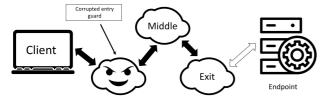

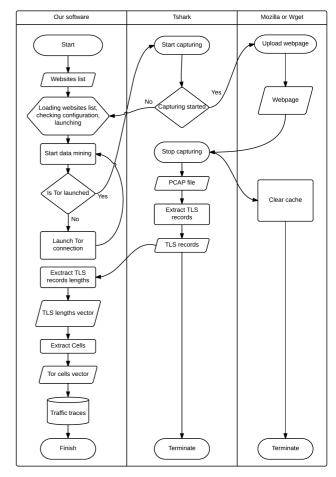

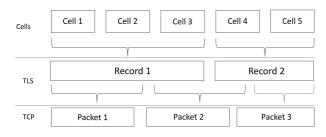

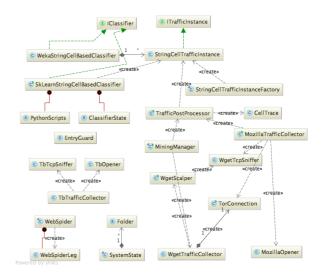

| System for Deep Web Users Deanonimization<br>A. Lazarenko, S. Avdoshin <sup>200</sup>                                                                                            |

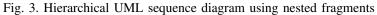

| Model of Security for Object-Oriented and Object-Attributed Applications<br><i>P. Oleynik, S. Salibekyan</i> 211                                                                 |

| Dynamic Key Generation According to the Starting Time<br>A. Kiryantsev, I. Stefanova-217                                                                                         |

| Investigating Concurrency in the Co-Simulation Orchestration Engine for INTO-CPS<br>C.T. Hansen, P.G. Larsen                                                                     |

| A Static Approach to Estimation of Execution Time of Components in AADL Models<br>A. Troitskiy, D. Buzdalov                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------|

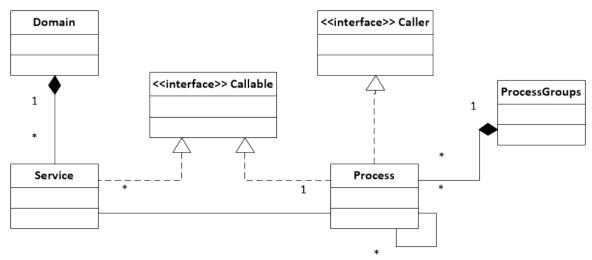

| Practical Experience of Software and System Engineering Approaches in Requirements Management for Software Development in Aviation Industry |

| I. Koverninskiy, A. Kan, V. Volkov, Yu. Popov, N. Gorelits236                                                                               |

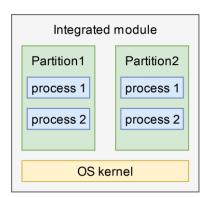

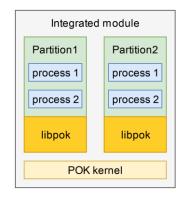

| Design and Architecture of Real-time Operating System<br>K. Mallachiev, N. Pakulin, A. Khoroshilov                                          |

| Developing a Debugger for Real-Time Operating System<br>A. Emelenko, K. Mallachiev, N. Pakulin                                              |

| Building and Testing an Embedded Operating System<br><i>A. Ovcharov, N. Pakulin</i>                                                         |

### Foreword

Dear participants, it is our pleasure to meet you at the  $10^{\text{th}}$  Anniversary Spring/Summer Young Researchers' Colloquium on Software Engineering (SYRCoSE). This year's colloquium is hosted by Moscow State University (MSU), one of the oldest (established in 1755 by M.V Lomonosov), biggest and most famous Russian universities. Graduates of the university greatly contributed to theoretical computer science, system programming, and software engineering. Among them are Professors A.P. Ershov (1931 – 1988), L.N. Korolev (1926 – 2016), V.V. Lipaev (1928 – 2015), A.A. Lyapunov (1911 – 1973), E.Z. Lyubimskiy (1931 – 2008), V.S. Shtarkman (1931 – 2005), M.R. Shura-Bura (1918 – 2008), V.F. Turchin (1931 – 2010), E.A. Zhogolev (1930 – 2003), and many others. SYRCoSE 2016 is organized by Institute for System Programming of the Russian Academy of Sciences (ISP RAS) jointly with Moscow and Saint-Petersburg Universities.

SYRCoSE 2016's Program Committee (consisting of more than 50 members from more than 25 organizations) has selected 38 papers. Each submitted paper has been reviewed independently by three referees. The authors and speakers represent well-known universities, research institutes and companies including Aarhus University, Aston, Cairo University, Higher School of Economics, Innopolis University, Institute for System Programming of the Russian Academy of Sciences, Kazan Federal University, Keldysh Institute of Applied Mathematics of the Russian Academy of Sciences, Lero – The Irish Software Research Centre, MCST, Moscow Institute of Physics and Technology, Moscow State University, Orenburg State University, Politecnico di Milano, Rostov State University of Civil Engineering, Saint-Petersburg State Polytechnic University, Saint-Petersburg State University, Southern Federal University, Ulyanovsk Technical State University, University of Passau, University of Southern Denmark, Volga Region State University of Telecommunication and Informatics (6 countries, 16 cities, and 25 organizations).

We would like to thank all of the participants of SYRCoSE 2016 and their advisors for interesting papers. We are also very grateful to the PC members and the external referees for their hard work on reviewing the papers and selecting the program. Our thanks go to the invited speakers, Dirk Beyer (University of Passau), Alexey Khoroshilov (ISP RAS), and Vartan Padaryan (ISP RAS). We would also like to thank our sponsors and supporters: Russian Foundation for Basic Research (grant 16-07-20256), Federal Agency of Scientific Organizations, Exactpro Systems, and EMC Research and Development Center LLC. Finally, our special thanks go to the local organizers, Eugene Kornykhin (MSU) and Arif Sultanov (Recreation Center 'Krasnovidovo', MSU), for their invaluable help in organizing the colloquium at MSU's Recreation Center 'Krasnovidovo'.

Sincerely yours,

Alexander S. Kamkin Alexander K. Petrenko Andrey N. Terekhov

May 2016

### Committees

### **Program Committee Chairs**

Alexander K. Petrenko – Russia Institute for System Programming of RAS

### **Program Committee**

|          | Jean-Michel Adam – France                                                                           |

|----------|-----------------------------------------------------------------------------------------------------|

|          | Pierre Mendès France University<br>Sergey M. Avdoshin – Russia                                      |

|          | Higher School of Economics                                                                          |

|          | Eduard A. Babkin – Russia<br>Higher School of Economics                                             |

|          | Nadezhda F. Bahareva – Russia                                                                       |

|          | Povolzhskiy State University of Telecommunications and Informatics<br>Svetlana I. Chuprina – Russia |

|          | Perm State National Research University                                                             |

|          | Pavel D. Drobintsev – Russia<br>Saint-Petersburg State Polytechnic University                       |

|          | Liliya Yu. Emaletdinova – Russia                                                                    |

|          | Kazan National Research Technical University<br>Victor P. Gergel – Russia                           |

|          | Lobachevsky State University of Nizhny Novgorod                                                     |

|          | Efim M. Grinkrug – Russia<br>Higher School of Economics                                             |

|          | Maxim L. Gromov – Russia                                                                            |

|          | Tomsk State University                                                                              |

|          | Vladimir I. Hahanov – Ukraine<br>Kharkov National University of Radioelectronics                    |

| <b>.</b> | Shihong Huang – USA                                                                                 |

|          | Florida Atlantic University<br>Iosif L. Itkin – Russia                                              |

|          | Exactpro Systems                                                                                    |

|          | Alexander S. Kamkin – Russia<br>Institute for System Programming of RAS                             |

|          | Andrei V. Klimov – Russia                                                                           |

|          | Keldysh Institute of Applied Mathematics of RAS                                                     |

|          | Vsevolod P. Kotlyarov – Russia<br>Saint-Petersburg State Polytechnic University                     |

|          | Alexander N. Kovartsev – Russia                                                                     |

|          | Samara State Aerospace University<br>Vladimir P. Kozyrev – Russia                                   |

|          | National Research Nuclear University "MEPhI"                                                        |

|          | Daniel S. Kurushin – Russia<br>State National Research Polytechnic University of Perm               |

| +-       | Peter G. Larsen – Denmark                                                                           |

|          | Aarhus University<br>Roustam H. Latypov – Russia                                                    |

|          | Kazan Federal University                                                                            |

|          | Alexander A. Letichevsky – Ukraine<br>Glushkov Institute of Cybernetics, NAS                        |

|          | Nataliya I. Limanova – Russia                                                                       |

|          | Povolzhskiy State University of Telecommunications and Informatics                                  |

|          | Alexander V. Lipanov – Ukraine<br>Kharkov National University of Radioelectronics                   |

|          | Irina A. Lomazova – Russia                                                                          |

|          | Higher School of Economics<br>Lyudmila N. Lyadova – Russia                                          |

|          | Higher School of Economics                                                                          |

|          | Vladimir A. Makarov – Russia<br>Yaroslav-the-Wise Novgorod State University                         |

|          | Victor M. Malyshko – Russia                                                                         |

|          | Moscow State University<br>Tiziana Margaria – Germany                                               |

|          | Lero – The Irish Software Research Centre                                                           |

| Orga     | anizing Committee                                                                                   |

Andrey N. Terekhov - Russia Saint-Petersburg State University

| Manual Massana Duasia                                                                |

|--------------------------------------------------------------------------------------|

| Manuel Mazzara – Russia<br>Innopolis University                                      |

| Marek Miłosz – Poland                                                                |

| Institute of Computer Science, Lublin University of Technology                       |

| Alexander S. Mikhaylov – Russia                                                      |

| Igor A. Minakov – Russia                                                             |

| Institute for the Control of Complex Systems of RAS                                  |

| Alexey M. Namestnikov – Russia                                                       |

| Ulyanovsk State Technical University<br>Valery A. Nepomniaschy – Russia              |

| Ershov Institute of Informatics Systems of SB of RAS                                 |

| Mykola S. Nikitchenko – Ukraine                                                      |

| Kyiv National Taras Shevchenko University                                            |

| Sergey P. Orlov – Russia                                                             |

| Samara State Technical University<br>Elena A. Pavlova – Russia                       |

| Microsoft                                                                            |

| Ivan I. Piletski – Belorussia                                                        |

| Belarusian State University of Informatics and Radioelectronics                      |

| Vladimir Yu. Popov – Russia                                                          |

| Ural Federal University<br>Yury I. Rogozov – Russia                                  |

| Taganrog Institute of Technology, Southern Federal University                        |

| Rustam A. Sabitov – Russia                                                           |

| Kazan National Research Technical University                                         |

| Nikolay V. Shilov – Russia                                                           |

| A.P. Ershov Institute of Informatics Systems of RAS<br>Ruslan L. Smelyansky – Russia |

| Moscow State University                                                              |

| Valeriy A. Sokolov – Russia                                                          |

| Yaroslavl Demidov State University                                                   |

| Petr I. Sosnin – Russia<br>Ulyanovsk State Technical University                      |

| Veniamin N. Tarasov – Russia                                                         |

| Povolzhskiy State University of Telecommunications and Informatics                   |

| Andrei N. Tiugashev – Russia                                                         |

| Samara State Aerospace University                                                    |

| Sergey M. Ustinov – Russia<br>Saint-Petersburg State Polytechnic University          |

| Vladimir V. Voevodin – Russia                                                        |

| Research Computing Center of Moscow State University                                 |

| Dmitry Yu. Volkanov – Russia                                                         |

| Moscow State University                                                              |

| Mikhail V. Volkov – Russia<br>Ural Federal University                                |

| Nadezhda G. Yarushkina – Russia                                                      |

| Ulyanovsk State Technical University                                                 |

| Rostislav Yavorsky – Russia                                                          |

| Higher School of Economics<br>Nina V. Yevtushenko – Russia                           |

| Tomsk State University                                                               |

| Vladimir A. Zakharov – Russia                                                        |

| Moscow State University                                                              |

| Sergey S. Zaydullin – Russia                                                         |

| Kazan National Research Technical University                                         |

Alexander S. Kamkin - Russia Institute for System Programming of RAS

### Referees

Ivan Andrianov Nikita Astrakhantsev Sergey Avdoshin Nadezhda Bahareva Oleg Borisenko Mikhail Chupilko Kyrylo Chykhradze Pavel Drobintsev Misha Drobyshevskii Mohamed Elwakil Victor Gergel Andrey Gomzin Efim Grinkrug Maxim Gromov Shihong Huang Iosif Itkin Leonard Johard Alexander Kamkin Mansur Khazeev Andrei Klimov Anton Korshunov Artem Kotsynyak Alexander Kovartsev Ilya Kozlov Vladimir Kozyrev Natalia Kushik Peter Gorm Larsen Roustam Latypov Mikhail Lebedev Irina Lomazova Jorge Lopez

Lyudmila Lyadova Victor Malyshko Vladimir Mayorov Manuel Mazzara Alexander Mikhaylov Alexey Namestnikov Yaroslav Nedumov Mykola Nikitchenko Sergey Orlov Alexander Petrenko Ivan Piletski Alexander Protsenko Delhibabu Radhakrishnan Nikolay Shilov Kirill Skorniakov Sergey Smolov Valeriy Sokolov Petr Sosnin Veniamin Tarasov Andrei Tatarnikov Alexander Tchitchigin Andrei Tiugashev Denis Turdakov Maksim Varlamov Dmitry Volkanov Mikhail Volkov Rostislav Yavorskiy Nina Yevtushenko Vladimir Zakharov Mark Zhitomirski

# Language Support for Generic Programming in Object-Oriented Languages: Design Challenges

Julia Belyakova

Institute for Mathematics, Mechanics and Computer Science named after I. I. Vorovich Southern Federal University Rostov-on-Don, Russia Email: julbel@sfedu.ru

Abstract—It is generally considered that object-oriented (OO) languages provide weaker support for generic programming (GP) as compared with such functional languages as Haskell or SML. There were several comparative studies which showed this. But many new object-oriented languages have appeared in recent years. Have they improved the support for generic programming? And if not, is there a reason why OO languages yield to functional ones in this respect? In the earlier comparative studies object-oriented languages were usually not treated in any special way. However, the OO features affect language facilities for GP and a style people write generic programs in such languages. In this paper we compare ten modern object-oriented languages and language extensions with respect to their support for generic programming. It has been discovered that every of these languages strictly follows one of the two approaches to constraining type parameters. So the first design challenge we consider is "which approach is better". It turns out that most of the explored OO languages use the less powerful one. The second thing that has a big impact on the expressive power of a programming language is support for multiple models. We discuss pros and cons of this feature and its relation to other language facilities for generic programming.

#### I. INTRODUCTION

Almost all modern programming languages provide language support for generic programming (GP) [1]. Some languages do it better than others. For example, Haskell is generally considered to be one of the best languages for generic programming [2, 3], whereas such mainstream objectoriented languages as C# and Java are much less expressive and have many drawbacks. There were several studies that compared language support for generic programming in different languages [2-5]. However, these studies do not make any difference between object-oriented and functional languages. We argue that OO languages are to be treated separately, because they support the distinctive OO features that pure functional languages do not, such as inheritance, interfaces/traits, subtype polymorphism, etc. These features affect the language design and a way people write generic programs in object-oriented languages.

Several new object-oriented languages have appeared in recent years, for instance, Rust, Swift, Kotlin. At the same time, several independent extensions have been developed for mainstream OO languages [6–9]. These new languages and extensions have many differences, but all of them tend to improve the support for generic programming. There is a lack of a careful comparison of the approaches and mechanisms for generic programming in *modern object-oriented* languages. This study is aimed to fill the gap: it gives a survey, analysis, and comparison of the facilities for generic programming that the chosen OO languages provide. We identify the dependencies between major language features, detect incompatible ones, and point the properties that a language design should satisfy to be effective for generic programming.

#### II. MAIN IDEAS

Ten modern object-oriented languages and language extensions have been explored in this study with respect to generic programming. We have found out that in the case of OO languages there are exactly two approaches to the design of language constructs for generic programming. We call the first one "constraints-are-types", because under this approach such OO constructs as interfaces or traits, which are usually used as types in object-oriented programs, are also used to constrain type parameters in generic programs. The second approach, "constraints-are-Not-types", restricts OO constructs to be used as types only, and provides separate language constructs for constraining type parameters. Hence the first design challenge arises: is one of this approaches better than another? Or the same expressive power can be achieved using any of them? We answer these questions in Sec. III. It turns out that the approaches cannot be integrated together, and the second one is more expressive.

The second point covered in the paper in detail (in Sec. IV) is language support for multiple models (by "model" we mean a way in which types satisfy constraints). There are several questions related to multiple models:

- 1) Is it desirable to have multiple models of a constraint?

- 2) How can support for multiple models be provided with the approaches we have discovered?

- 3) Why does not Haskell allow multiple models (instances of a type class)?

- 4) Is there a language design that reflects the support for multiple models better than the existing ones?

The short answers are:

```

interface IPrintable { string Print(); }

void PrintArr(IPrintable[] xs)

{ foreach (var x in xs)

Console.WriteLine("{0}\n", x.Print()); }

string InParens<T>(T x) where T : IPrintable

{ return "(" + x.Print() + ")"; }

```

Fig. 1. An ambiguous role of C# interfaces

- 1) Yes, it is desirable.

- 2) It can be naturally provided with the second approach but not with the first one.

- 3) Because of type inference.

- 4) Yes, there is.

In conclusion, we present a modified version of the wellknown table [2, 4] showing the levels of language support for the features important for generic programming. Table I provides information on all of the object-oriented languages considered, introduces some new features, and demonstrates the relations between the features.

### III. TWO APPROACHES TO CONSTRAINING TYPE PARAMETERS

This section provides a survey of *language constructs for generic programming* in several modern *object-oriented* programming languages as well as some language extensions. All of the languages we explored adopt one of the two approaches:

- Interface-like constructs, which are normally used as types in object-oriented programming, are also used to constrain type parameters. By "interface-like constructs" we mean, in particular, C#/Java interfaces, Scala traits, Swift protocols, Rust traits. Fig. 1 shows a corresponding example in C#: IPrintable interface acts as the type of xs in PrintArr, whereas in the function InParens<T> it is used to constrain the type parameter T.

- 2) For constraining type parameters a separate language construct is provided; such construct cannot be used as a type. We will see some examples in Sec. III-B.

Sec. III-A analyses the languages of the first category; Sec. III-B is devoted to the second one. In Sec. III-C we compare both approaches and answer the question "Which one is better if any?".

#### A. Languages with "Constraints-are-Types" Philosophy

C# and Java are probably the best-known programming languages in this category. Note that an interface (or a similar language construct) describes properties, an interface of a *single* type that implements/extends it. This has inevitable consequence: *multi-type constraints* (constraints on several types) cannot be expressed naturally. Consider a generic unification algorithm [10]: it takes a set of equations between terms (symbolic expressions), and returns the most general substitution which solves the equations. So the algorithm operates on three kinds of data: terms, equations, substitutions. A signature of the algorithm might be as follows:

```

Substitution Unify<Term, Equation, Substitution>

(IEnumerable<Equation>)

```

| <pre>interface ITerm<tm> { IEnumerable<tm> Subterms(); }</tm></tm></pre>       |

|--------------------------------------------------------------------------------|

| <pre>interface IEquation<tm, eqtn,="" subst=""></tm,></pre>                    |

| where Tm : ITerm <tm></tm>                                                     |

| <pre>where Eqtn : IEquation<tm, eqtn,="" subst=""></tm,></pre>                 |

| <pre>where Subst : ISubstitution<tm, eqtn,="" subst=""></tm,></pre>            |

| <pre>{ Subst Solve();   IEnumerable<eqtn> Split(); }</eqtn></pre>              |

| <pre>interface ISubstitution<tm, eqtn,="" subst=""></tm,></pre>                |

| where Tm : ITerm <tm></tm>                                                     |

| <pre>where Eqtn : IEquation<tm, eqtn,="" subst=""></tm,></pre>                 |

| where Subst : ISubstitution <tm, eqtn,="" subst=""></tm,>                      |

| { Tm SubstituteTm(Tm);                                                         |

| <pre>IEnumerable<eqtn> SubstituteEq (IEnumerable<eqtn>); }</eqtn></eqtn></pre> |

Fig. 2. The C# interfaces for unification algorithm

| interfa | <b>ace</b> IComparab | <pre>ple<t> { int CompareTo(T other); }</t></pre> |  |

|---------|----------------------|---------------------------------------------------|--|

| class : | SortedSet <t></t>    | where T : IComparable <t> {}</t>                  |  |

|         |                      |                                                   |  |

Fig. 3. The <code>IComparable<T></code> interface in C#

But a bunch of functions has to be provided to implement the algorithm: Subterms : Term  $\rightarrow$  IEnumerable<Term>,

Solve : Equation  $\rightarrow$  Substitution,

SubstituteTm : Substitution  $\times$  Term  $\rightarrow$  Term,

SubstituteEq : Substitution × IEnumerable<Equation>

$\rightarrow$  IEnumarable<Equation>, and some others. All these functions are needed for unification at once, hence it would be convenient to have a single constraint that relates all the type parameters and provides the functions required.

Substitution Unify<Term, Equation, Substitution>

(IEnumerable<Equation>) where <single constraint>

But in C#/Java the only thing one can do<sup>1</sup> is to define three different interfaces for Term, Equation, and Substitution, and then separately constrain every type parameter with a respective interface. Fig. 2 shows the interface definitions. To set up a relation between mutually dependent interfaces, three type parameters are used: Tm for terms, Eqtn for equations, and Subst for substitution. Moreover, the parameters are repeatedly constrained with the appropriate interface in every interface definition. That constraints are to be stated in a signature of the unification algorithm as well:

```

Subst Unify<Tm, Eqtn, Subst> (IEnumerable<Eqtn>)

where Tm : ITerm<Tm>

where Eqtn : IEquation<Tm, Eqtn, Subst>

where Subst : ISubstitution<Tm, Eqtn, Subst>

```

There is one more thing to notice here — interfaces are used in both roles in the same piece of code: the IEnumerable<Eqtn> interface is used as a type, whereas other interfaces in the where sections are used as constraints.

The problem of multi-type constraints is a common thing for OO languages in the first category, but C# and Java have various drawbacks besides that [2, 8]. In comparison with other programming languages that support generic programming (not only object-oriented), these are much less expressive. An incomplete list of drawbacks is enumerated below.

<sup>&</sup>lt;sup>1</sup>The Concept design pattern can also be used, but it has its own drawbacks. We will discuss concept pattern later, in Sec. IV-C2.

- Lack of retroactive interface implementation. After the type had been defined, it cannot implement any new interface. A consequence is that a generic code with constraints on type parameters can only be instantiated with types *originally* designed to satisfy these constraints. It is impossible to adapt the type afterwards, even if it semantically conforms the constraints.

- Drawbacks of F-bounded polymorphism. F-bounded polymorphism [11] allows "recursive" constraints (Fconstraints) on type parameters in the form T : I<T>, where T is a type parameter, I <> is a generic interface. Such kind of constraints solves the binary method problem [12]: Fig. 3 demonstrates a corresponding C# [13] example. The type parameter T in the interface IComparable<T> pretends to be a type that implements this interface. This is indeed the case for the class SortedSet<T> due to the constraint T : IComparable<T>, so the method T.CompareTo(T) is like a binary function for comparing elements of type T. But the semantics of IComparable<T> itself has nothing to do with binary methods. One could easily write some class F00 implementing IComparable<Bar>, and thus the semantics of comparing two Bars would be broken. Another shortcoming of F-bounded polymorphism is that a code with recursive constraints is rather cumbersome and difficult to understand. Yet, as we will see, F-bounded polymorphism is not the only solution for the binary method problem. More detailed discussion on pitfalls of F-bounded polymorphism can be found in [8] and [14].

- Lack of associated types [14, 15]. Types that are logically related to some entity are often called associated types of the entity. For instance, types of edges and vertices are associated types of a graph. There is no specific language support for associated types in C# and Java: such types are expressed in generic code in the form of extra type parameters.

- Lack of constraints propagation [14, 15]. Look at the following code:

```

void baz<T>(SortedSet<T> s)

where T : IComparable<T> { ... }

```

The function baz<T> takes a value of the type SortedSet<T>; in the definition of SortedSet<T> in Fig. 3 the type parameter T, type of elements, is constrained with IComparable<T>. In the baz<T> definition T has to be also constrained, otherwise the code would not compile: a compiler does not propagate the constraints implied by formal parameters, that is a programmer's burden.

Some of these drawbacks were eliminated in modern objectoriented languages. In the following subsections we briefly examine language facilities for generic programming in the modern OO languages with "constraint-are-types" philosophy.

1) Interfaces in Ceylon and Kotlin: In contrast to C#, Ceylon [16] and Kotlin [17] interfaces support *default method implementation*, so Java 8 [18] interfaces do. This is a useful feature for generic programming. For instance, one

```

interface Equatable<T> {

fun equal (other: T) : Boolean

fun notEqual(other: T): Boolean

{

return !this.equal(other) }}

class Ident (name : String) : Equatable<Ident> {

val idname = name.toUpperCase()

override fun equal (other: Ident) : Boolean

{

return idname == other.idname }}

```

Fig. 4. Interfaces and constraints in Kotlin

| shared interface Comparable <other> of Other</other>      |   |

|-----------------------------------------------------------|---|

| given Other satisfies Comparable <other></other>          | { |

| <pre>shared formal Integer compareTo(Other other);</pre>  |   |

| <pre>shared Integer reverseCompareTo(Other other) {</pre> |   |

| <pre>return other.compareTo(this); }</pre>                | } |

Fig. 5. The use of "self type" in Ceylon interfaces

struct Point { x: i32, y: i32, }

...

impl Point {

fn moveOn(&self, dx: i32, dy: i32) -> Point

{ Point {x: self.x + dx, y: self.y + dy } }}

...

impl Point {

fn reflect(&self) -> Point

{ Point {x: -self.x, y: -self.y} }}

...

let p1 = Point {x: 4, y: 3};

let p2 = p1.moveOn(1, 1); let p3 = p1.reflect();

Fig. 6. Point struct and its methods in Rust

can define an interface for equality that provides a default implementation for inequality operation. Fig. 4 demonstrates corresponding Kotlin definitions: the Ident class implements the interface Equatable<Ident> that has two methods, equal and notEqual; as long as notEqual has a default implementation in the interface, there is no need to implement it in the Ident class. In addition to default method implementations, the Ceylon language also allows to declare a type parameter as a self type. An example is shown in Fig. 5. In the definition of the Comparable<Other> interface the declaration of Other explicitly requires other to be a self type of the interface, i.e. a type that implements this interface. Because of this the reverseCompareTo method can be defined: the other and this values have the type Other, with the Other implementing Comparable<Other>, so the call other.compareTo(this) is perfectly legal.

2) Scala Traits: Similarly to advanced interfaces in Java 8, Ceylon, and Kotlin, Scala traits [5, 19] support *default method implementations*. They can also have *abstract type* members, which, in particular, can be used as *associated types* [20]. Just as in C#/Java/Ceylon/Kotlin, type parameters (and abstract types) in Scala can be constrained with traits and supertypes (upper bounds): the latter constraints are called *subtype constraints*. But, moreover, they can be constrained with subtypes (lower bounds), which is called *supertype constraints* respectively. None of the languages we discussed so far support supertype constraints nor associated types. Another important Scala feature, implicits [19], will be mentioned later in Sec. IV-A with respect to the Concept design pattern.

```

trait Eqtbl { fn equal(&self, that: &Self) -> bool;

fn not_equal(&self, that: &Self) -> bool

{ !self.equal(that) }}

trait Printable { fn print(&self); }

...

impl Eqtbl for i32 {

fn equal (&self, that: &i32) -> bool { *self == *that }}

...

struct Pair<S, T>{ fst: S, snd: T }

...

impl <S : Eqtbl, T : Eqtbl> Eqtbl for Pair<S, T> {

fn equal (&self, that: &Pair<S, T>) -> bool

{self.fst.equal(&that.fst) && self.snd.equal(&that.snd)}}

```

Fig. 7. An example of using Rust traits

3) Rust Traits: Rust language [21] quite differs from other object-oriented languages. There is no traditional class construct in Rust, but instead it suggests structs that store the data, and separate method implementations for structs. An example is shown in Fig. 6<sup>2</sup>: two impl Point blocks define method implementations for the Point struct. If a function takes the  $\texttt{sself}^3$  argument (as moveOn), it is treated as a method. There can be any number of implementation blocks, yet they can be defined at any point after the struct declaration (even in a different module). This gives a huge advantage with respect to generic programming: any struct can be *retroactively* adapted to satisfy constraints.

Constraints in Rust are expressed using traits. A trait defines which methods have to be implemented by a type similarly to Scala traits, Java 8 interfaces, and others. Traits can have *default method implementations* and *associated types*; besides that, a *self type* of the trait is directly available and can be used in method definitions. Fig. 7<sup>4</sup> demonstrates an example: the Eqtbl trait defining equality and inequality operations. Note how support for self type solves the binary method problem (here equal is a binary method): there is no need in extra type parameter that "pretends" to be a self type, because the self type self is already available.

Method implementations in Rust can be probably thought of similarly to .NET "extension methods". But in contrast to .NET<sup>5</sup>, types in Rust also can *retroactively implement traits* in impl blocks as shown in Fig. 7: Eqtbl is implemented by i32 and Pair<S, T>. The latter definition also demonstrates a so-called *type-conditional implementation*: pairs are equality comparable only if their elements are equality comparable. The constraint <S : Eqtbl... is a shorthand, it can be declared in a where section as well.

There is no struct inheritance and subtype polymorphism in Rust. Nevertheless, as long as traits can be used not only as constraints but also as types, a dynamic dispatch is provided through a feature called trait objects. Suppose i32 and f64

<sup>2</sup>Some details were omitted for simplicity. To make the code correct, one has to add #[derive(Debug,Copy,Clone)] before the Point definition.

<sup>3</sup>The "&" symbol means that an argument is passed by reference.

<sup>4</sup>Some details were omitted for simplicity. The following declaration is to be provided to make the code correct: #[derive(Copy, Clone)] before the definition struct Pair<S : Copy, T : Copy>. Yet the type parameters of the impl for pair must be constrained with Copy+Equatable.

<sup>5</sup>Similarly to .NET, Kotlin supports extending classes with methods and properties, but interface implementation in extensions is not allowed.

implement the Printable trait from Fig. 7. Then the following code demonstrates creating and use of a polymorphic collection (the type of the polyvec elements is a reference type):

let pr1 = 3; let pr2 = 4.5; let pr3 = -10; let polyVec: Vec<&Printable> = vec![&pr1, &pr2, &pr3]; for v in polyVec { v.print(); }

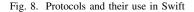

4) Swift Protocols: Swift is a more conventional OO language than Rust: it has classes, inheritance, and subtype polymorphism. Classes can be extended with new methods using extensions that are quite similar to Rust method implementations. Instead of interfaces and traits Swift provides protocols. They cannot be generic but support associated types and same-type constraints, default method implementations through protocol extensions, and explicit access to the self type; due to the mechanism of extensions, types can retroactively adopt protocols. Fig. 8 illustrates some examples: the Equatable protocol extended with a default implementation for notEqual (pay attention to the use of the self type); the contains<T> generic function with a protocol constraint on the type parameter T; an extension of the type Int that enables its conformance to the Printable protocol; the Container protocol with the associated type ItemTy; the allItemsMatch generic function with the same-type constraint on types of elements of two containers, C1 and C2.

#### B. Languages with "Constraints-are-Not-Types" Philosophy

Most of the languages in this category were to some extent inspired by the design of Haskell type classes [22]. For defining constraints these languages suggest *new language constructs*, which are usually second-class citizens<sup>6</sup>. These constructs have *no self types* and *cannot* be used as types, they describe requirements on type parameters in external way; therefore, retroactive constraints satisfaction (*retroactive modeling*) is automatically provided. Besides retroactive modeling, an integral advantage of such kind of constructs is that *multitype constraints* can be easily and naturally expressed using them; yet there is no semantic ambiguity which arises when the same construct, such as C# interface, is used both as a type and constraint, as in the example below:

void Sort<T>(ICollection<T>) where T : IComparable<T>;

Here ICollection<T> and IComparable<T> are generic interfaces, but the former is used as a type whereas the latter is used as constraint.

<sup>&</sup>lt;sup>6</sup>Second-class citizens cannot be assigned to variables, passed as arguments, returned from functions.

```

interface EO { boolean eq(This that);

boolean notEq(This that); }

abstract implementation EQ [EQ] {

boolean notEq(This that) { return !this.eq(that); }}

boolean contains<X>(List<X> list, X x)

where X implements EQ { ... }

abstract class Expr {...} class IntLit extends Expr {...}

class PlusExpr extends Expr { Expr left; Expr right; ... }

implementation EQ [Expr] {

boolean eq(Expr that) { return false; }}

implementation EQ [PlusExpr] {boolean eq(PlusExpr that) {...}}

interface UNIFY [Tm, Eqtn, Subst] {

{ IEnumerable<Tm> Subterms(); ... }

receiver Tm

receiver Eqtn { IEnumerable<Eqtn> Split(); ... }

receiver Subst { Tm SubstituteTm(Tm); ...

}}

Subst Unify<Tm, Eqtn, Subst>(Enumerable<Eqtn>)

where [Tm, Eqtn, Subst] implements UNIFY {...}

```

Fig. 9. Generalized interfaces in JavaGI

1) JavaGI Generalized Interfaces: JavaGI [6] generalized interfaces represent a kind of confluence of both "constraintsare-types" and "constraints-are-*not*-types" philosophies. Such interfaces as PrettyPrintable defined below are called single-parameter interfaces. They describe an interface of a single type and can be used both as types and constraints.

interface PrettyPrintable { String prettyPrint(); }

Such interfaces have explicit access to the *self type* named This; an example is shown in Fig. 9, where the self type is used in the interface EQ. There is no direct support for default method implementations in JavaGI, but *abstract implementation definitions* can be used for this purpose<sup>7</sup>. For example, the notEq method of EQ (Fig. 9) is implemented in such a way. Generalized interfaces can be implemented *retroactively* in implementation blocks. They do not support associated types but can be generic; moreover, implementations can be generic as well, and support for *type-conditional interface implementation* is provided:

```

implementation<br/><S, T> EQ [Pair<S, T>] where S implements EQ where T implements EQ { ... }

```

Besides single-parameter interfaces, there are *multi-headed* generalized interfaces that adopt several features from Haskell type classes [23] and describe interfaces of several types. There is no self type in a multi-headed interface; therefore, it cannot be used as a type, it is designed to be used as a constraint *only*. An example of multi-headed interface is shown in Fig. 9: the UNIFY interface contains all the functions required by the unification algorithm considered earlier; the requirements on three types (term, equation, substitution) are defined at once in a single interface. Note how succinct is this definition as compared with the one in Fig. 2.

2) Language G and C++ concepts: Concept as an explicit language construct for defining constraints on type parameters was initially introduced in 2003 [24]. Several designs have

```

concept InputIterator<Iter> { type value; ... }

concept Monoid<T> { fun identity_elt() -> T;

fun binary_op(T, T) -> T; };

model Monoid<int>

{ fun identity_elt() -> int@ { return 0; } ... };

fun accumulate<Iter> where { InputIterator<Iter>,

Monoid<InputIterator<Iter>.value> }

(Iter first, Iter last) -> InputIterator<Iter>.value> }

{ let init = identity_elt(); ... }

```

| Fig. 10. Concepts and their use in |

|------------------------------------|

|------------------------------------|

been developed since that time [25–27]; in the large, the expressive power of concepts is rather close the Haskell type classes [3]. Concepts were to solve the problems of unconstrained C++ templates [14, 28]; they were expected to be included in C++0x standard, but this did not happen. A new version of concepts, Concepts Lite (C++1z) [29], is under way now. The language G declared as "a language for generic programming" [7] also provides concepts that are very similar to the C++0x concepts. G is a subset of C++ extended with several constructs for generic programming. For "C++ concepts" we use the G syntax in this paper.

Similarly to a type class, a concept defines a set of requirements on one or more type parameters. It can contain *function signatures* that may be accompanied with *default implementations, associated types*, nested *concept-requirements* on associated types, and *same-type constraints*. A concept can *refine* one or more concepts, it means that refining concept includes all the requirements from the refined concepts. Refinement is very similar to multiple interface inheritance in C# or protocol inheritance in Swift. Due to the concept refinement, a so-called *concept-based overloading* is supported: one can define several versions of an algorithm/class that have different constraints, and then at compile time the most specialized version is chosen for the given instance. The C++ advance algorithm for iterators is a classic example of concept-based overloading application.

It is said that a type (or a set of types) *satisfies* a concept if an appropriate model of the concept is defined for this type (types). Model definitions are independent from type definitions, so the modeling relation is established *retroactively*; models can be generic and *type-conditional*. Fig. 10 illustrates some examples: the InputIterator<Iter> concept with the associated type of elements value; the Monoid<T> concept and its model for the type int; the accumulate<Iter> generic function with two constraints, on the type of an iterator and on the associated type of this iterator. Note how identity\_elt is called in accumulate: in contrast to the languages from the previous section, identity\_elt is available in the body of accumulate at the top-level; this may lead to some inconvenience even if the autocomplete feature is supported in IDE.

3) C# with concepts: In the C#<sup>cpt</sup> project [8] (C# with concepts) concept mechanism integrates with subtyping: type parameters and associated types can be constrained with *super-types* (as in basic C#) and also with *subtypes* (as in Scala). In contrast to all of the languages we discussed earlier, C#<sup>cpt</sup> allows *multiple models* of a concept in the same scope. Some ex-

<sup>&</sup>lt;sup>7</sup>The design of JavaGI we discuss here goes back to 2011 when default method implementations were not supported in Java. With Java 8 this task could probably be solved in a more elegant way.

```

concept CEquatable[T] { bool Equal(T x, T y);

bool NotEqual(T x, T y) { return !Equal(x, y); }}

interface ISet<T> where CEquatible[T] { ... }

model default StringEqCaseS for CEquatable[String] { ... }

model StringEqCaseIS for CEquatable[String] { ... }

bool Contains<T>(IEnumerable<T> values, T x)

where CEquatable[T] using CEq { ... if (cEq.Equal(...) ... }

Fig. 11. Concepts and models in C#cpt

```

```

constraint Eq[T] { boolean T.equals(T other); }

constraint GraphLike[V, E] { V E.source(); ... }

interface Set[T where Eq[T]] { ... }

model CIEq for Eq[String] { ... } // case-insensitive model

model DualGraph[V,E] for GraphLike[V,E]

where GraphLike[V,E] g

V E.source() { return this.(q.sink)(); } ... }

```

Fig. 12. Constraints and models in Genus

amples are shown in Fig. 11: the CEquatable [T] concept with the Equal signature and a default implementation of NotEqual, the generic interface ISet<T> with concept-requirement on the type parameter T, and two models of CEquatable[] for the type string — for case-sensitive and case-insensitive equality comparison. The first model is marked as a *default* model<sup>8</sup>: it means that this model is used if a model is not specified at the point of instantiation. For instance, in the following code StringEqCaseS is used to test strings equality in s1.

```

ISet<String> s1 = ...;

ISet<String>[using StringEqCaseIS] s2 = ...;

s1 = s2; // Static ERROR, s1 and s2 have different types

```

Note that s1 and s2 have different types because they use different models of CEquatible[String]. This property is called "constraints-compatibility" in [8], but we will refer to it as "models-consistency". One more interesting thing about C#cpt: concept-requirements can be named. In the Contains<T> function (Fig. 11) the name *cEq* is given to the requirement on T; this name is used later in the body of Contains<T> to access the Equal function of the concept. It is also worth mention that the interface IEnumerable<T> is used as a type along with the concept CEquatable[T] being used as a constraint; thus, the role of interfaces is not ambiguous any more, interfaces and concepts are independently used for different purposes.

4) Constraints in Genus: Like G concepts and Haskell type classes, constraints in Genus [9] (an extension for Java) are used as constraints only. Fig. 12 demonstrates some examples: the Eq[T] constraint, which is used to constrain the T in the Set[T] interface; the model of Eq[String] for caseinsensitive equality comparison; the multi-parameter constraint GraphLike[V, E], and the type-conditional generic model DualGraph[V,E]. Methods in Genus classes/interfaces can impose additional constraints:

<sup>8</sup>The default model can be generated automatically for a type if the type conforms to a concept, i.e. it provides methods required by the concept.

interface List[E] { boolean remove(E e) where Eq[E]; ... }

Here the List[] interface can be instantiated by any type, but the remove method can be used only if the type E of elements satisfies the Eq[E] constraint. This feature is called model genericity.

Just as C#cpt, Genus supports multiple models and automatic generation of the *natural* model, which is the same thing as the default model in C#<sup>cpt</sup>. Due to this, the following code causes a static type error (we saw the same example in C#<sup>cpt</sup>):

```

Set[String] s1 =

Set[String with CIEq] s2 = ...;

s1 = s2; // Static ERROR, s1 and s2 have different types

```

In Genus this feature is called model-dependent types. An important note is to be made here: in contrast to true dependent types that depend on values, model-dependent types depend on models, which are compile-time artefacts. So the modeldependent types are just as dependent as generic types are type-dependent types.

As well as concept-requirements in C#cpt, constraintrequirements in Genus can be named; the example is shown in Fig. 12: g is a name of the GraphLike[V,E] constraint required by the DualGraph[V,E] model. Because function signatures inside constraints are declared with an explicit receiver type (in a style close to JavaGI), such as the type T in the Eq[T] constraint, syntax of calls to functions in the case of named models is \_. (g.sink) (), not g.sink(\_).

#### C. Which Philosophy Is Better If Any?

It is time to find out which approach is better. Taking into consideration what we explored in Sec. III-A and Sec. III-B, we draw a conclusion that there are only two language features that cannot be incorporated in a language together:

- 1) the use of a construct both as a type and constraint;

- 2) natural support for multi-type constraints.

Languages with "constraints-are-types" philosophy support the first feature but not the second, languages with "constraintsare-Not-types" philosophy vice versa<sup>9</sup>. Can we determine one feature that is more important?

It was shown in the study [30] that in practice interfaces that are used as constraints (such as IComparable<T> in C# or Comparable<X> in Java) are almost never used as types:

<sup>&</sup>lt;sup>9</sup>JavaGI seems to support both of them, but it actually provides different constructs for different purposes: single-parameter interfaces are more like Rust traits or Swift protocols, whereas multi-headed interfaces are similar to concepts and type classes; the latter cannot be used as types.

authors had checked about 14 millions lines of Java code and found only one such example, and, furthermore, it was rewritten and eliminated. It is also mentioned in [30] that the same observation holds for the code in Ceylon.

It is hard to imagine any useful "constraint-and-type" example besides the IPrintable interface from Fig. 1. In those rare cases when this could happen, it is possible to provide a lightweight language mechanism for automatic generation of one construct from another. For example, single-parameter Genus constraints with some restrictions could be translated to Java interfaces, with the other direction being easier. At the same time, multi-type constraints, which can be so naturally expressed under the "constraints-are-Not-types" approach, have rather awkward and cumbersome representation in the "constraints-are-types" approach. All other language facilities we discussed could be supported under any approach. Therefore, we claim that the "constraints-are-Not-types" approach is preferable. An additional benefit is that it eliminates the ambiguity in semantics of the interface-like constructs.

#### IV. SINGLE MODEL VERSUS MULTIPLE MODELS

For simplicity, in this part of the paper we call "constraint" any language construct that is used to describe constraints, while a way in which types satisfy the constraints we call "model". We have seen in the previous section that most of the languages allow to have only one, unique model of a constraint for the given set of types; only C#<sup>cpt</sup> [8] and Genus [9] support multiple models<sup>10</sup>. And indeed this makes sense for the languages with "constraints-are-types" philosophy, because it is not clear what to do with types that could implement interfaces (or any other similar constructs) in several ways. But how does this affect generic programming?

It turns out that sometimes it is desirable to have multiple models of a constraint for the same set of types. The example of string sets with case-sensitive and case-insensitive equalities we saw earlier is one of such examples; another one is the use of different orderings, yet different graph implementations, and so on. Thus, in respect of generic programming, the absence of multiple models is rather a problem than a benefit. Without extending the language the problem of multiple models can be solved in two ways:

- 1) Using the Adapter pattern. If one wants the type Foo to implement IComparable<Foo> in a different way, an adapter of Foo, the Foo1 that implements IComparable<Foo1> can be created. This adapter then can be used instead of Foo whenever the Foo1-style comparison is required. An obvious shortcoming of this approach is the need to repeatedly wrap and unwrap Foo values; in addition, a code becomes cumbersome.

- 2) Using the Concept pattern, which is considered in Sec. IV-A.

Both approaches have serious drawbacks. Moreover, as we have discovered in Sec. III-C, languages with the "constraints-are-types" philosophy are in the large less expressive than ones

```

// F-bounded polymorphism

interface IComparable<T> { int CompareTo(T other); }

void Sort<T>(T[] values) where T : IComparable<T> { ... }

class SortedSet<T> where T : IComparable<T> { ... }

// Concept Pattern

interface IComparer<T> { int Compare(T x, T y); }

void Sort<T>(T[] values, IComparer<T> cmp) { ... }

class SortedSet<T> { private IComparer<T> cmp; ... }

public SortedSet(IComparer<T> cmp) { ... } ... }

```

Fig. 13. The use of the Concept design pattern in C#

with the "constraints-are-Not-types" philosophy. But may such languages as C#<sup>cpt</sup> and Genus, which are in the "constraintsare-Not-types" category and support multiple models at the language level, be considered as the best languages for generic programming, or we can imagine a language with a better design? And one more question: if language support for multiple models is a good idea, then why does not Haskell [23] allow multiple instances of a type class? After all, it is considered to be one of the most expressive languages for generic programming. We answer the latter question in Sec. IV-B and discuss the former one in Sec. IV-C.

#### A. Concept Pattern

The Concept design pattern is suitable for programming languages with the "constraints-are-types" philosophy. It eliminates two problems:

- 1) Firts, it enables *retroactive modeling* of constraints, which is not supported in such languages as C#, Java, Ceylon, Kotlin, or Scala.

- 2) Second, it allows to define *multiple models* of a constraint for the same set of types.

The idea of the Concept pattern is as follows: instead of constraining type parameters, generic functions and classes take extra arguments that provide a required functionality — "concepts". Fig. 13 shows an example: in the case of the Concept pattern the F-constraint T : IComparable<T> is replaced with an extra argument of the type IComparer<T>. The IComparer<T> interface represents a concept of comparing: it describes the interface of an object that can compare values of the type T. As long as one can define several classes implementing the same interface, different "models" of the IComparer<T> "concept" can be passed into Sort<T> and SortedSet<T>.

This pattern is widely used in generic libraries of such mainstream object-oriented languages as C# and Java; it is also used in Scala. Due to implicits [5, 19], the use of the Concept pattern in Scala is a bit easier: in most cases an appropriate "model" can be found by a compiler implicitly, so there is no need to explicitly pass it at a call site<sup>11</sup>. Nevertheless, the pattern has two substantial drawbacks. First of all, it brings *run-time overhead*, because every object of a generic class with constraints has at least one extra field for the "concept", while generic functions with constraints take at least one

<sup>&</sup>lt;sup>10</sup>G [7] allows multiple models only in different lexical scopes.

<sup>&</sup>lt;sup>11</sup> Scala is often blamed for its complex rules of implicits resolution: sometimes it is not clear which implicit object is to be used.

extra argument. The second drawback, which we call *models-inconsistency*, is less obvious but may lead to very subtle errors. Suppose we have s1 of the type HashSet<String> and s2 of the *same* type, provided that s1 uses case-sensitive equality comparison, s2 — the case-insensitive one. Thus, s1 and s2 use different, inconsistent models of comparison. Now consider the following function:

```

static HashSet<T> GetUnion<T>(HashSet<T> a, HashSet<T> b)

{    var us = new HashSet<T>(a, a.Comparer);

us.UnionWith(b); return us; }

```

Unexpectedly, the result of GetUnion(s1, s2) could differ from the result of GetUnion(s2, s1). Despite the fact that s1 and s2 have the same type, they use different comparers, so the result depends on which comparer was chosen to build the union. Recall that in C#<sup>cpt</sup> and Genus models are part of the types; therefore, the similar situation causes a static type error. But in the case of the Concept pattern modelsconsistency *cannot* be checked at *compile time*.

#### B. Instance Uniqueness in Haskell

Type classes in Haskell [22] provide a support for ad hoc polymorphism (function overloading). Like concepts and constraints, they define functions available for some types. For instance, a type class for equality comparison is defined as follows:

It contains a function signature for equality operator ==, and provides a default implementation for inequality operator /=. Then instances (models) of this type class can be defined for types. For example, an instance for Int, a *type-conditional* instance for lists, and so on.

instance Eq Int where ... -- (==) implementation instance Eq a => Eq [a] where ... -- (==) implementation

As long as type classes support ad hoc polymorphism, they are "globally transparent". If a function is a part of some type class, every time the name of this function is used a compiler knows that an instance of the corresponding type class must be provided. And there is a strong reason why multiple instances of a type class for the same set of types are not allowed in Haskell: it is *type inference*. Consider the following function definition:

foo xs ys = if xs == ys then xs else xs ++ ys

In Haskell such definition is valid and its type can be inferred. It is  $Eq a \Rightarrow [a] \rightarrow [a]^{12}$ . Inference succeeds, because a compiler knows the following facts: as long as (++) has the type  $[a] \rightarrow [a] \rightarrow [a]$ , xs and ys are lists; there is an instance of Eq for lists (Eq  $a \Rightarrow Eq$  [a]). If there were no Eq [a] instance available, type checking would fail.

Now suppose that multiple instances of a type class are allowed. What to do with type inference of the  $f_{00}$  in this case? To check whether there is at least one instance Eq [a]? And what if we also have the following code:

```

class Eq a => Baz a where

bar :: a -> Int

useBar x y = if length x > length y then bar x - bar y

else bar y - bar x

```

If instances are uniquely defined, type checker just checks if there is an instance Eq [a] that implies Baz [a] (x and y are inferred to be lists because length has the type [a] -> Int). But if there are multiple Eq [a] instances, then every Baz [a] instance must specify which Eq [a] instance it uses. It can even be the case that there is a Baz [a] instance for one Eq [a], but not for another one. Therefore, at the point of the useBar *definition* a compiler has no idea whether there is an error of missed instance or not, because it knows nothing about the instances that might be used in a call to useBar. This information is available only at the point of a *call*.

Note that even with the OverlappingInstances extension for Haskell, multiple models in a sense we discuss in the paper are not supported. This extension indeed allows to have several instances that match the constraints deduced for a code. But there must be only one instance among them that compiler can select unambiguously (according to some rules) at the point of a code *definition*. Again, not at the call site — at the point of definition. Thus, a user of the code still cannot choose between instances, an instance is already selected by a compiler. Thus, Haskell sacrifices language support for multiple models for the sake of type inference. It is a strong argument for Haskell users, but in the case of the most objectoriented programming languages, which usually do not allow to omit type annotations of function arguments as well as constraints on type parameters, there is no need to prohibit multiple models in OO languages.

#### C. Parameters versus Predicates

So far we have discovered that languages with "constraintsare-Not-types" philosophy, if they also allow to define multiple models, may potentially provide better support for generic programming compared to other languages. We have seen only two languages with such properties,  $C\#^{cpt}$  [8] and Genus [9], and there is an essential shortcoming in the design of both of them: constraints on type parameters are declared in "predicate-style" rather than "parameter-style". For example, consider the following Genus definition [9]:

SSSP[V, E, W] is a function for Dijkstras single-source shortestpath algorithm, with the GraphLike[V, E], Weighted[E, W], OrdRing[W] and Hashable[V] being constraints on type parameters. The constraints look as if they were predicates on types, and if they were predicates, this function would probably be well-designed. For example, in Haskell, G, C#, Java, Rust, and many other languages, where only one model of a constraint is allowed for the given set of types, constraints on type parameters are indeed predicates: types either satisfy the constraint (if they have a model that is unique) or not. But in Genus and C#<sup>cpt</sup> constraints *are not predicates*, they are

<sup>&</sup>lt;sup>12</sup>[a] is a type of generic list, it is a notation for Data.List a

actually *parameters*, as long as different models of constraints can be used. In the worst case a call to SSSP[V, E, W] would be as follows:

Whereas in the best case:

...pathFromX = SSSP[MyVert, MyEdge, Double](x);

Note that edge and weight types cannot be deduced, because they are determined by models of the constraints, not by the vertex  $\times$  itself. It is easy to imagine that models of edge weighing and its ordered ring would often vary, so a call to SSSP[V, E, W] is likely to look like this in many cases:

This is not very bad but is also not good enough.

If look again at the SSSP algorithm, one could notice that it really depends on three things: a source vertex, a model of a weighed graph which this vertex belongs to, and a model of hashing. Furthermore, at the level of the SSSP signature the type E of edges does not matter, we are interested in the model of weighed graph as a whole. Taking into account this ideas, we can rewrite the SSSP in the following way:

```

constraint WeighedGraph[V,E,W]

extends GraphLike[V,E], Weighted[E,W], OrdRing[W] {}

Map[V,W] SSSP[V,E,W](V s)

where WeighedGraph[V,E,W], Hashable[V] { ... }

```

Then a call to SSSP also becomes better:

...pathFromX = SSSP[MyVert, MyEdge, Double with MyWGr](x);

Nevertheless, we believe that in the case of multiple models the "predicate-style" of constraints is misleading and makes it more difficult to write and call a generic code. We suggest that the design of constraints has to be in the "parameter-style". One example of such design is provided by the extension for the OCaml language — *modular implicits* [31]; it is briefly discussed in Sec. IV-C1. A sketch of the "parameter-style" design of constraints for object-oriented languages is presented in Sec. IV-C2.

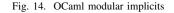

1) Modular Implicits in OCaml: In the "modular implicits" extension for the OCaml language [31] module types are used to describe constraints, modules represent models, with generic functions explicitly taking module-parameters. Fig. 14 demonstrates some examples. By contrast to concepts and genus constraints, module types and modules do not have type parameters, instead they have type members, such as the t in the Eq module type. Eq\_int and Eq\_list are models of Eq for the int and generic list. Generic functions that need constraints, such as foo and foo', explicitly take implicit module parameters EL and E. Notice that just as type parameters, EL and E are *compile-time* parameters, not runtime. They are called implicit because at a call to generic function actual models can be inferred, as in the x and yexamples in Fig. 14. Notice that in the foo function any model of comparison of lists is expected, whereas foo' expects a

```

module type Eq = sig

type t

val equal : t -> t -> bool

end

implicit module Eq_int = struct

type t = int

let equal x y = ...

end

implicit module Eq_list {E : Eq} = struct

type t = Eq.t list

let equal xs vs = ...

end

let foo {EL : Eq} xs ys = if EL.equal(xs, ys)

then xs else xs @ vs

= if (Eq_list E).equal(xs, ys)

let foo' {E : Eq} xs vs

then xs else xs @ vs

let x = foo [1;2;3] [4;5]

let y = foo' [1;2;3] [4;5]

```

```

concept Equality[T] { bool Equal(T x, T y);

bool NotEqual(T x, T y) { return !Equal(x, y); }}

concept Ordering[T] refines Equality[T]

{ int Compare(T x, T y); }}

interface ISet<T | Equality[T] eq> { ... }

interface ICollection<T> { ...

bool Remove<Equality[T] eq>(T x); ... }

bool Contains<T | Equality[T] eq>(IEnumerable<T> vs, T x)

{... if (eq.Equal(...) ...}

int MaxInt<|Ordering[int] ord>(IEnumerable<int> vs) {...}

```

Fig. 15. The use of concept-parameters in Cp#

model of comparison of elements of lists and fixes the model  ${\tt Eq\_list}$   ${\tt E}$  of comparison of lists.

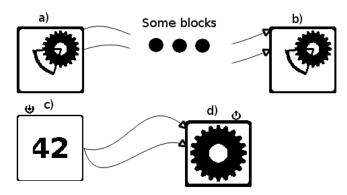

2) Concept Parameters for C#: Fig. 15 shows some examples of a generic code in the style of concept-parameters, which we call Cp# — C# with concept-Parameters. Concepts are the same as in C#<sup>cpt</sup>, whereas constraints on type parameters are not predicates any more, they are explicitly stated as *parameters* in the angle brackets after the "|" sign. In the ICollection<T> interface the Remove method is obviously generic: it takes the concept-parameter eq for comparing the values of the type T. Note that concept-parameters can even be non-generic as in the MaxInt function.

If default models are supported, it must be possible to infer concept-arguments just in the same way as in C# or Genus, so that instances of generic functions and classes can be written in a usual way, without the need to specify the models required:

```

var ints = new ISet<int>(...);

var has5 = Contains(ints, 5);

var maxv = MaxInt(ints);

var minv = MaxInt<|IntOrdDesc>(ints);

ISet<String> s1 = ...;

ISet<String|StringEqCaseIS> s2 = ...;

s1 = s2; // Static ERROR, s1 and s2 have different types

```

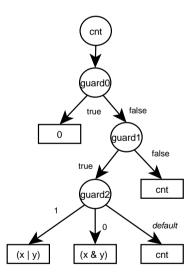

C#<sup>cpt</sup> and Genus can easily be redesigned to follow the "concept-parameters style" presented here. With this style the syntax of such languages would perfectly fit the semantics. On the other hand, the "concept-predicates style" misleads a

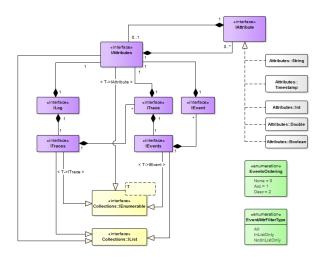

|                                            | Haskell    | C#         | Java 8 | Scala | Ceylon | Kotlin   | Rust | Swift | JavaGI         | G                | $C \#^{cpt}$ | Genus     | ModImpl    |

|--------------------------------------------|------------|------------|--------|-------|--------|----------|------|-------|----------------|------------------|--------------|-----------|------------|

| Constraints can be used as types           | 0          | ٠          | •      | •     | •      | •        | •    | ٠     | O              | 0                | 0            | 0         | 0          |

| Explicit self types                        | -          | $^{\circ}$ | 0      | O     | •      | 0        | ۲    | ۲     | O              | _                | -            | -         | -          |

| Multi-type constraints                     | ٠          | $\star$    | ×      | *     | 0      | $\star$  | 0    | 0     | ٠              | ٠                | ٠            | ٠         | ٠          |

| Retroactive type extension                 | _          | •          | 0      | 0     | 0      | •        | ٠    | •     | 0              | 0                | 0            | 0         | _          |

| Retroactive modeling                       | •          | $\star$    | ×      | ×     | 0      | $\times$ | •    | •     | •              | ٠                | •            | •         | •          |

| Type conditional models                    | •          | 0          | 0      | 0     | 0      | 0        | ٠    | 0     | ۲              | ٠                | ٠            | ٠         | ٠          |

| Static methods                             | $igodot^a$ | 0          | •      | 0     | ٠      | •        | •    | ٠     | •              | $igodot^a$       | $\bullet^a$  | $ullet^a$ | $igodot^a$ |

| Default method implementation              | ٠          | 0          | •      | ٠     | ٠      | •        | •    | •     | O              | •                | ٠            | 0         | 0          |

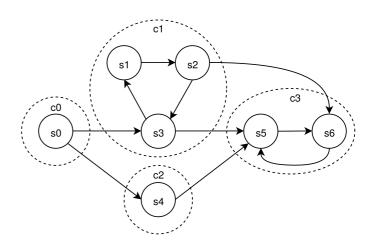

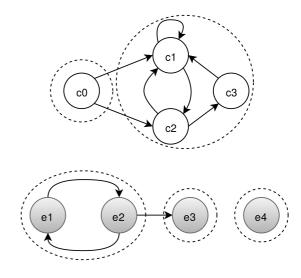

| Associated types                           | •          | 0          | 0      | •     | 0      | 0        | •    | •     | 0              | •                | •            | 0         | •          |

| Constraints on associated types            | 0          | —          | -      | •     | _      | -        | ٠    | •     | _              | ٠                | •            | -         | ۲          |

| Same-type constraints                      | O          | -          | -      | ٠     | -      | -        | ٠    | •     | -              | ٠                | •            | -         | ٠          |

| Subtype constraints                        | _          | ٠          | •      | ٠     | •      | •        | _    | •     | 0              | 0                | •            | 0         | _          |

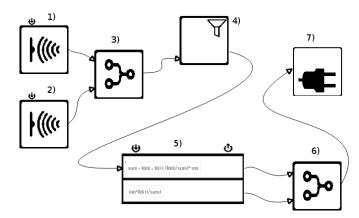

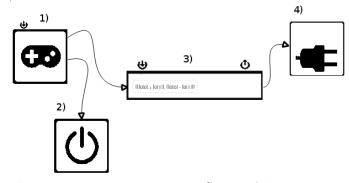

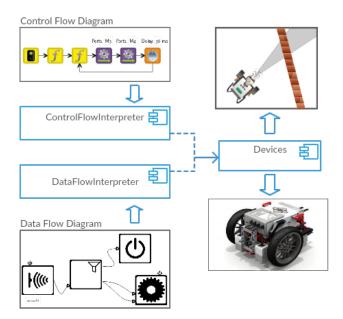

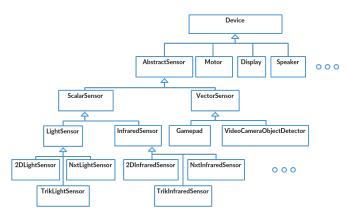

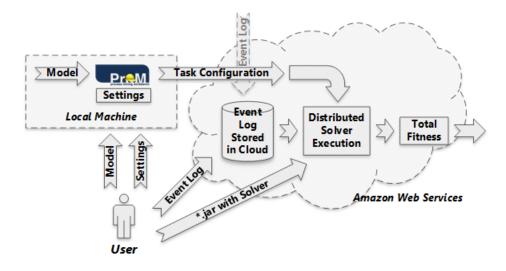

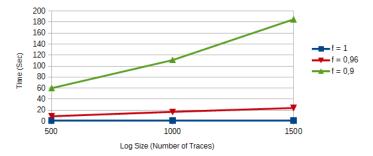

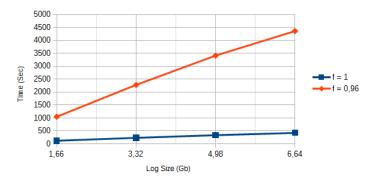

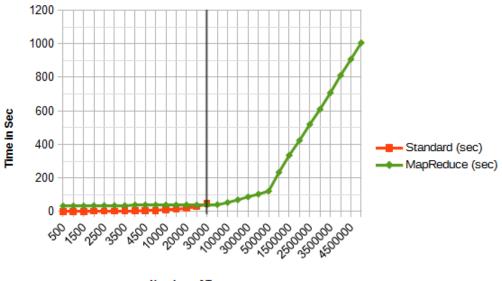

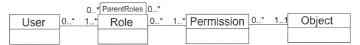

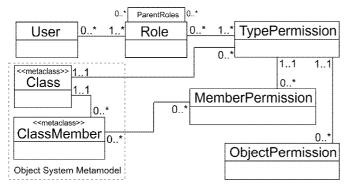

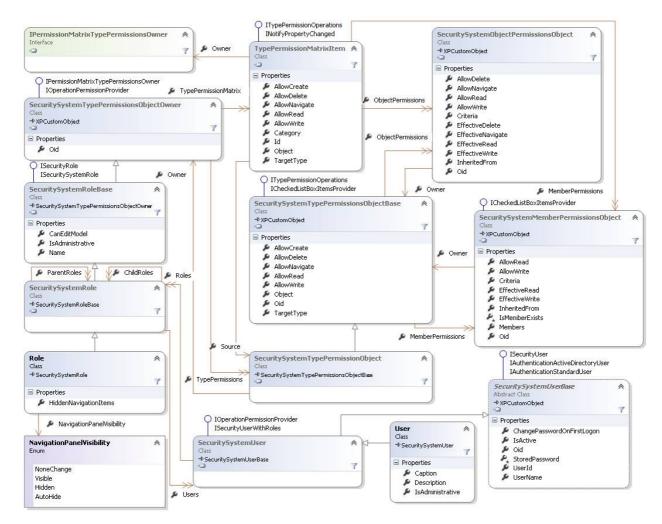

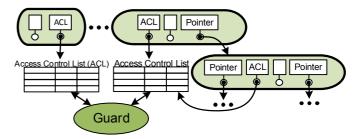

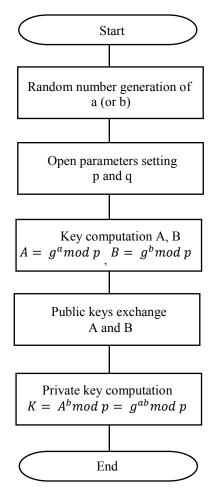

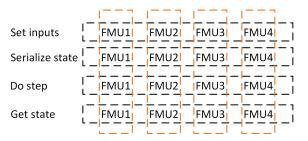

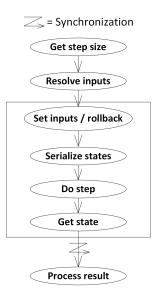

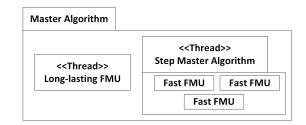

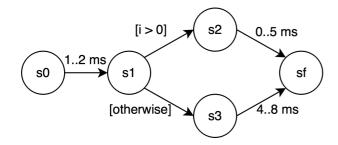

| Supertype constraints                      | -          | 0          | 0      | ٠     | 0      | 0        | -    | 0     | 0              | 0                | •            | 0         | -          |